6.2寸液晶屏 800*480分辨率 RGB接口

型号:H062HWV60E5001

尺寸:6.2 inch

分辨率: 800(RGB) × 480

接口方式:60pin 24bit RGB

外观尺寸(显示区域):120.7*75.8*2.8(108 x 64.80)

亮度:500 nits

Service hotline:138-2870-9518(Mr Yang)

Support customization

Quality assurance

Brand certification

Current location:Home > Product Center > Products

型号:H062HWV60E5001

尺寸:6.2 inch

分辨率: 800(RGB) × 480

接口方式:60pin 24bit RGB

外观尺寸(显示区域):120.7*75.8*2.8(108 x 64.80)

亮度:500 nits

Support customization

Quality assurance

Brand certification

Product parameters

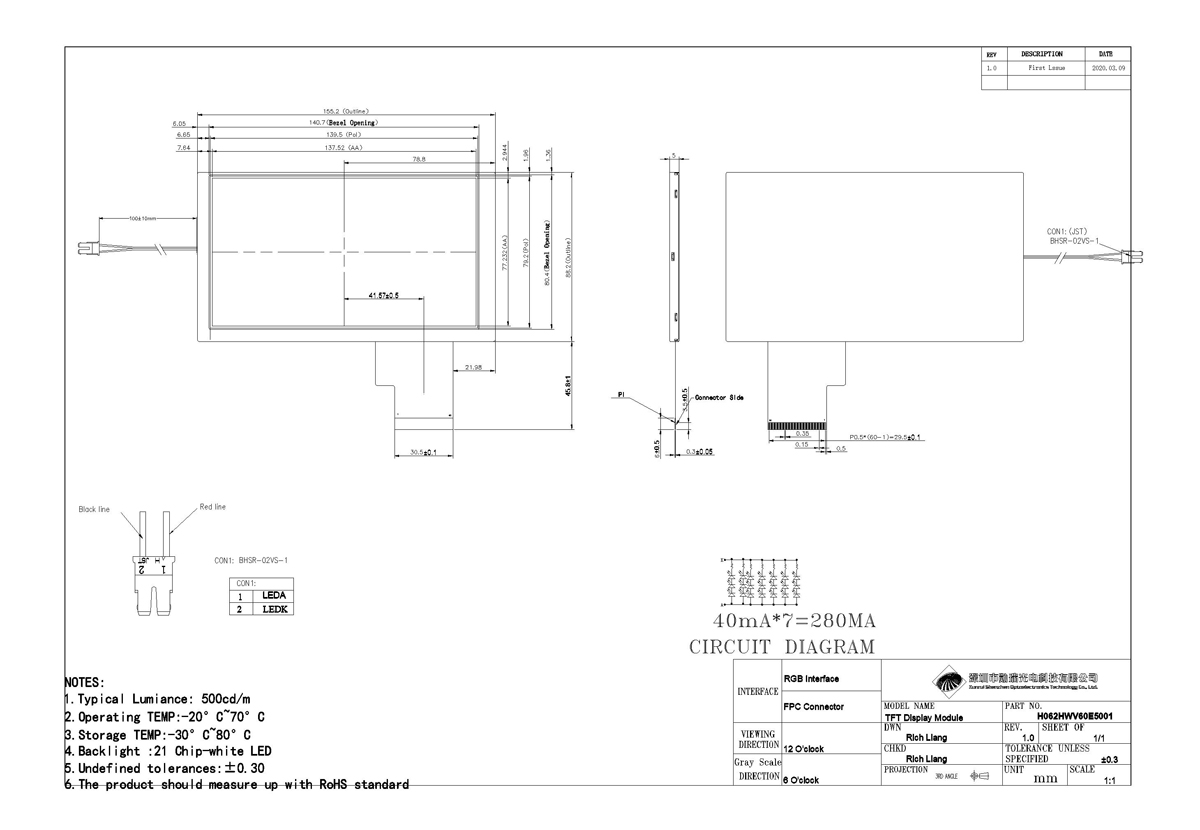

产品图纸

一、产品参数:

Size | 6.2 inch |

Resolution | 800(horizontal)*480(Vertical) |

Interface | 24-bit RGB |

Connect type | Connector |

Color Depth | 16.7M |

Technology type | a-Si |

Pixel pitch (mm) | 0.1719 x 0.1609 |

Pixel Configuration | R.G.B. Vertical Stripe |

Display Mode | Normally White |

- | |

Luminance | 500 nits |

Viewing Direction | 12 O’clock |

Gray Scale Inversion Direction | 6 O’clock |

LCM (W x H x D) (mm) | 155.2X88.2X5 |

Active Area(mm) | 137.52x 77.232 |

With /Without TSP | Without |

Weight (g) | TBD |

LED Numbers | 21LEDs (3S7P) |

二、产品接口定义:

No. | Symbol | Description |

1 | AGND | Analog Ground |

2 | AVDD | Analog Power |

3 | VCC | Digital Power |

4~11 | R0~R7 | Data Input |

12~19 | G0~G7 | Data Input |

20~27 | B0~B7 | Data Input |

28 | DCLK | Clock input |

29 | DE | Data Enable signal |

30 | HSD | Horizontal sync input. Negative polarity |

31 | VSD | Vertical sync input. Negative polarity |

32 | MODE3 | DE/SYNC mode select .normally pull high H:DE Mode L:HSD/VSD mode |

33 | RSTB | Global reset pin. Active low to enter reset state. suggest to Connecting with an RC reset circuit for stability .normally pull High. |

34 | STBYB | standby mode, normally pull high STBYB="1",normal operation STBYB="0",timming control ,source driver will turn off, all output are high-Z |

35 | SHLR | Source right or left sequence control. SHLR="L", shift left: last data=S1<-S2…S1200=first data SHLR="H", shift right: first data=S1->SS2…S1200=last data |

36 | VCC | Digital Power |

37 | UPDN | Gate up or down scan control. UPDN="L" , DOWN shift : G1->G2…->G480 ; UPDN="H", up shift: G1<-G2…<-G480 |

38 | GND | Digital Ground |

39 | AGND | Analog Ground |

40 | AVDD | Analog Power |

41 | VCOM | For external VCOM DC input (Adjustable) |

42 |

DITH | Dithering setting: DITH="H" 6bit resolution (last 2 bits of input data truncated) (default setting) DITH="L" 8bit resolution |

43~44 | NC | Not connect |

45 | V10 | Gamma correction voltage reference |

46 | V9 | Gamma correction voltage reference |

47 | V8 | Gamma correction voltage reference |

48 | V7 | Gamma correction voltage reference |

49 | V6 | Gamma correction voltage reference |

50 | V5 | Gamma correction voltage reference |

51 | V4 | Gamma correction voltage reference |

52 | V3 | Gamma correction voltage reference |

53 | V2 | Gamma correction voltage reference |

54 | V1 | Gamma correction voltage reference |

55 | NC | Not connect |

56 | VGH | Positive Power for TFT |

57 | VCC | Digital Power |

58 | VGL | Negative Power for TFT |

59 | GND | Digital Ground |

60 | NC | Not connect |

三、产品尺寸图纸

推荐产品

MORE+